Samsung Electronics ha annunciato di aver avviato la produzione di chipset con processo produttivo a 3 nanometri (nm) applicando l’architettura a transistor Gate-All-Around (GAA). L’azienda ha iniziato con la produzione di chip semiconduttori per applicazioni di calcolo ad alte prestazioni ma prevede di espandersi più avanti ai processori mobile.

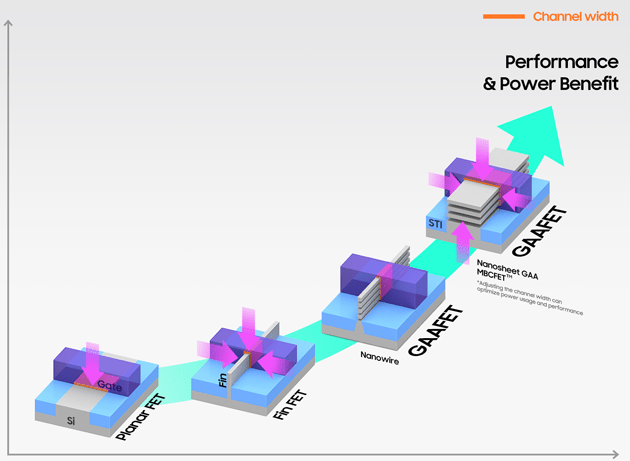

Multi-Bridge-Channel FET (MBCFET), la tecnologia GAA di Samsung implementata per la prima volta in assoluto, sfida i limiti prestazionali della tecnologia FinFET, migliorando l’efficienza energetica riducendo il livello di tensione di alimentazione, e migliorando al contempo le prestazioni aumentando la capacità della corrente di azionamento.

“Samsung è cresciuta rapidamente mentre continuiamo a dimostrare la leadership nell’applicazione di tecnologie di nuova generazione alla produzione, come il primo High-K Metal Gate del settore della fonderia, FinFET e EUV. Cerchiamo di continuare questa leadership con il primo processo a 3 nm al mondo con MBCFET”, ha affermato il Dr. Siyoung Choi, Presidente e Head of Foundry Business di Samsung Electronics. "Continueremo l’innovazione attiva nello sviluppo tecnologico competitivo e costruiremo processi che aiutano ad accelerare il raggiungimento della maturità della tecnologia".

La tecnologia proprietaria di Samsung utilizza nanosheet con canali più ampi per prestazioni più elevate e una maggiore efficienza energetica rispetto alle tecnologie GAA che utilizzano nanowire con canali più stretti. Utilizzando la tecnologia GAA a 3nm, Samsung ha la possibilità di regolare la larghezza del canale del nanosheet per ottimizzare il consumo energetico e le prestazioni per soddisfare le diverse esigenze dei clienti.

Inoltre, la flessibilità di progettazione di GAA è altamente vantaggiosa per la Design Technology Co-Optimization (DTCO), che aiuta ad aumentare i vantaggi di potenza, prestazioni e area (PPA). Rispetto al processo a 5nm, Samsung dice che il processo a 3nm di prima generazione può ridurre il consumo energetico fino al 45%, migliorare le prestazioni del 23% e ridurre l’area del 16% rispetto a 5nm, mentre il processo a 3nm di seconda generazione serve a ridurre il consumo energetico fino a al 50%, migliora le prestazioni del 30% e riduce l’area del 35%.

Confronto di performance e benefici energetici di Planar Fet, FinFet, GAAFET (nanowire) e GAAFET (MBCFET)

Man mano che i nodi tecnologici diventano più piccoli e le esigenze di prestazioni dei chip aumentano, i progettisti di circuiti integrati devono affrontare la sfida di gestire grandi quantità di dati per verificare prodotti complessi con più funzioni e scalabilità più ridotta. Per soddisfare questo tipo di esigenze, Samsung si è impegnata a fornire un ambiente di progettazione più stabile per ridurre il tempo necessario per il processo di progettazione, verifica e approvazione, aumentando al contempo l’affidabilità del prodotto. Dal terzo trimestre del 2021, Samsung Electronics ha fornito un’infrastruttura di progettazione collaudata attraverso un’ampia preparazione con i partner Samsung Advanced Foundry Ecosystem (SAFE), tra cui Ansys, Cadence, Siemens e Synopsys, per aiutare i clienti a perfezionare il proprio prodotto in un periodo di tempo ridotto.

“Insieme, Ansys e Samsung continuano a fornire tecnologia abilitante per progetti più avanzati, ora a 3nm con tecnologia GAA. La fedeltà all’approvazione della nostra piattaforma di simulazione multifisica Ansys testimonia la nostra continua collaborazione con Samsung Foundry all’avanguardia. Ansys rimane impegnata a fornire la migliore esperienza di progettazione per i nostri clienti avanzati comuni" ha dichiarato John Lee, Vice President and General Manager of the Electronics, Semiconductor & Optics Business Unit di Ansys.

“Siemens EDA è lieta di aver collaborato con Samsung per garantire che le nostre piattaforme software esistenti funzionino anche sul nuovo nodo di processo a 3 nanometri di Samsung sin dalla fase di sviluppo iniziale. La nostra partnership di lunga data con Samsung attraverso il programma SAFE genera un valore significativo per i nostri clienti comuni, grazie alla certificazione degli strumenti EDA Siemens leader del settore a 3nm" ha commentato Joe Sawicki, Executive Vice President for the IC-EDA segment of Siemens Digital Industries Software di Siemens EDA.

“Grazie alla nostra collaborazione strategica di lunga data con Samsung Foundry, stiamo consentendo alle nostre soluzioni di supportare i processi avanzati di Samsung, aiutando i nostri clienti comuni ad accelerare significativamente i loro cicli di progettazione. Il nostro supporto per il processo a 3nm di Samsung con architettura GAA continua ad espandersi, ora con i nostri prodotti Synopsys Digital Design, Analog Design e IP, consentendo ai clienti di fornire SoC differenziati per applicazioni chiave di calcolo ad alte prestazioni." ha commentato Shankar Krishnamoorthy, General Manager and Corporate Staff for the Silicon Realization Group di Synopsys.

foto credit: Samsung Electronics / in copertina: stabilimento di produzione di chipset a 3nm Samsung Foundry